this part and if we analyse this circuit it becomes like a common source amplifier, where the load it is diode connected.

So, the circuit becomes like this. We do have  $g_{m1}$ , we do have  $g_{m7}$  connected to  $V_{DD}$  and then this transistor half of the transistor we may call say  $M_3$  by 2. It is just a just a matter of representation and at this point we are giving the small signal along with the DC. Of course, this node it is getting the bias similar to this point and we like to know what will be the corresponding output here due to the small signal and this small signal it is  $v_{in\_c}$ .

Now, if you analyse this circuit or if you draw the small signal equivalent circuit, you can find that the voltage here  $v_{o2} = - g_{m1} \times \frac{1}{1+g_{m1}(2r_{o3})}$ . So, this into whatever input signal we are applying  $v_{in\_c}$ . In fact, as I said the voltage here also it will be same.

So, we may say that  $v_{o1}$  under common mode operation is also  $= v_{o2}$  and that gives us  $v_{o\_c} = v_o$  common mode. And hence the corresponding common mode gain if I say  $A''_C$

which is defined by  $\frac{v_{o\_c}}{v_{in\_c}} = - g_{m1} \times \frac{1}{1+g_{m1}(2r_{o3})}$ .

Now, again you can see here because the resistance now it is getting changed  $\frac{1}{g_{m7}}$ . So, this  $A_C$  it is much smaller than the previous common mode gain. So, to summarize what we can see the advantage of having this current mirror in the load part.

(Refer Slide Time: 46:11)

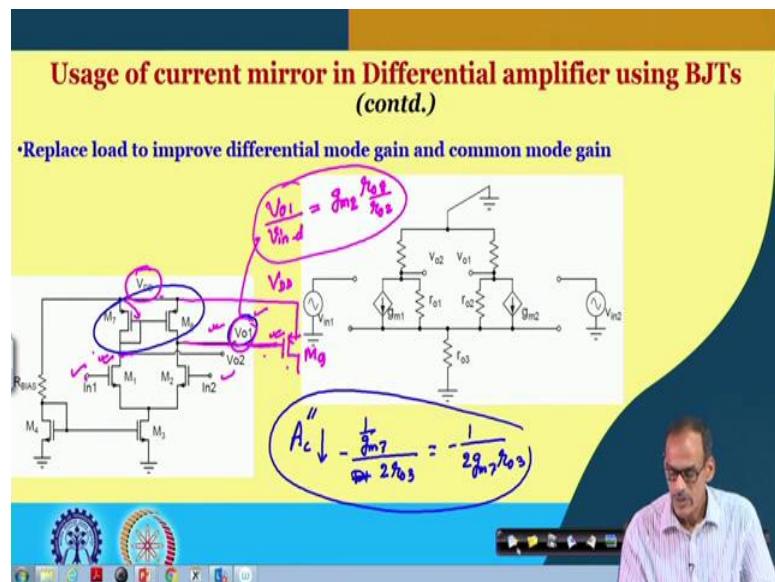

What do we obtain it is the common mode gain got drastically decreased and it =  $-\frac{1}{g_{m7}}$  divided by 1 plus sorry, one part we can remove so,  $\times 2r_{o3}$ . So, that =  $-\frac{1}{2g_{m7}r_{o3}}$ .

So, this is one consequence of having this active current mirror load and the gain at this point, gain at this point if I say that  $\frac{v_{o1}}{v_{in\_d}}$ . So, that is becoming  $g_{m1} \left( \frac{r_{o8}}{r_{o2}} \right)$ . In fact, you may say  $g_{m1}$  or  $g_{m2}$  both are same. So, we can say that differential input to single ended output gain it is same as whatever the gain earlier you obtained.

So, that is why this circuit it is very popular to convert differential signal in the form of common mode signal in addition to that since the DC voltage here it is same for the two nodes the DC voltage here it can be directly obtained from this node and since this DC voltage it is with respect to  $V_{DD}$  or to be more precise it is  $V_{DD} - V_{SG7}$ . So, we can say that DC voltage here it is  $V_{DD} - V_{SG7}$  and hence this voltage can directly be used to bias PMOS transistor in the subsequent stage.

So, we can have this is  $V_{DD}$  and let you call this is transistor-9 and this 9 transistor-9, it is having a very meaningful DC voltage received from on the previous drain node of transistor-8 and of course, it is also receiving the signal which is coming through this  $v_{o1}$ . I think most of the things I have covered.

(Refer Slide Time: 48:52)

Let me summarize the presentation in these 3 parts of this lecture what we have done it is we have started with a small signal small signal model of current mirror particularly, under DC condition as well as whenever it is carrying the signal current for both BJT and MOSFET versions.

And then after that we have talked about usage of current mirror particularly as bias elements for common emitter amplifier and common source amplifier particularly for the load part and we have seen that it enhance the gain of the both the amplifiers. And then also we have discussed about the usage of current mirror as a biasing element for common collector and common drain amplifier. And then finally, we have talked about usage of current mirror in differential amplifier.

And it is having two kinds of application, one is for biasing element and we have seen that it improves the common mode gain and differential mode gain. In addition to that finally, we have talked about the usage of the current mirror as active mirror load. This helps to convert the output port in the form of single ended and in addition it also decrease the common mode gain what we said is  $A''_C$  very low it is in fact, it is magnitude it is  $\frac{1}{2} g_m r_{o3}$ , this is very very small.

So, this helps to improve the common mode rejection drastically. I think that is all to cover. In the next class we will be talking about numerical examples.

Thank you for listening.